# Capítulo 8 **Temporizador 555**

circuito integrado (CI) 555 é utilizado basicamente como temporizador, astável e biestável em diversas aplicações industriais e em projetos simples com finalidades educativas. Esse dispositivo foi desenvolvido inicialmente como NE-5555 pela Signetics na decada de 1970. Hoje é fabricado por mais empresas, como a Fairchild (NE555), a National Semiconductor (LM555), a Motorola (MC1555), a Philips (NE555), a RCA (CA555) e a Sanyo (LC7555).

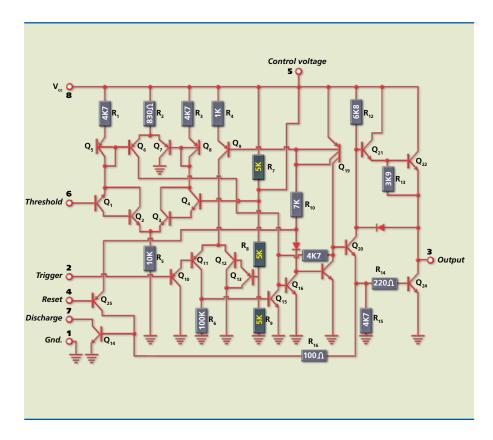

Dentro do envoltório que condiciona esse dispositivo, há 23 transistores, dois diodos e 16 resistores (figura 8.1).

**Figura 8.1** Circuito interno do CI 555.

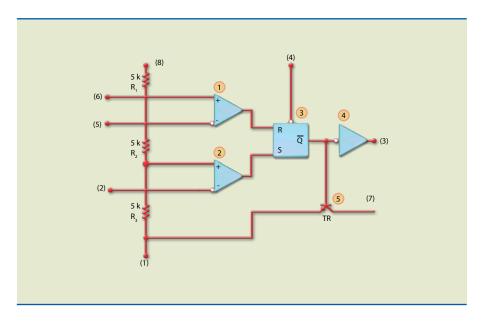

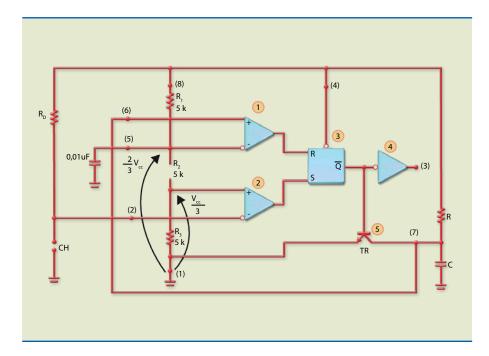

Para entendermos o funcionamento desse circuito, vamos usar o diagrama de blocos da figura 8.2, uma vez que é quase impossível fazer uma análise pelo esquema do circuito interno.

**Figura 8.2**Diagrama de blocos do Cl 555.

Os pinos do dispositivo 555 são representados pelos terminais numerados de 1 a 8 na figura 8.2 e apresentam as seguintes finalidades:

- 1. GND (terra).

- 2. Trigger (disparo).

- 3. Saída.

- 4. Reset.

- 5. Control (controle de tensão).

- **6.** *Threshold* (limiar).

- 7. Descarga.

- 8. V<sub>CC</sub>.

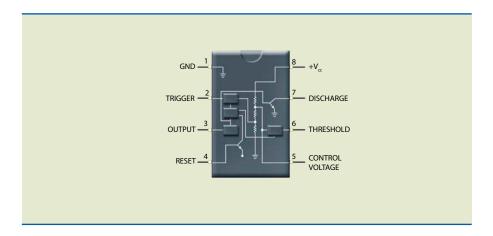

Entre os vários tipos de encapsulamento para esse dispositivo, o mais utilizado é o DIP (*dual in line package*) de quatro pares de pinos (figura 8.3a.)

Figura 8.3

Esquema de encapsulamento DIP de oito pinos.

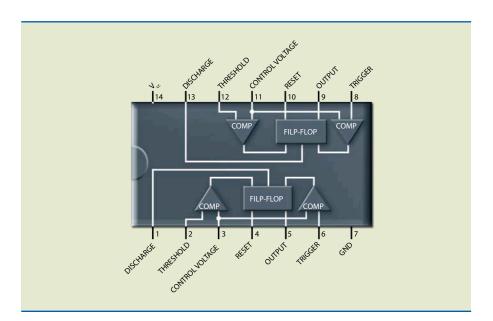

Existe um dispositivo, denominado 556, que armazena no encapsulamento dois circuitos integrados 555 (figura 8.4). Essa versão tem 16 pinos.

**Figura 8.4** Dispositivo 556, com dois circuitos integrados 555.

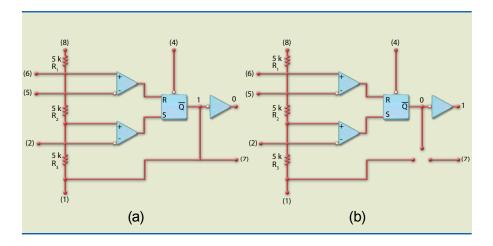

Retomando a figura 8.2, podemos observar o divisor constituído por três resistores de 5 k $\Omega$ . Foram esses componentes que deram origem ao nome 555.

Os blocos indicados nessa figura são:

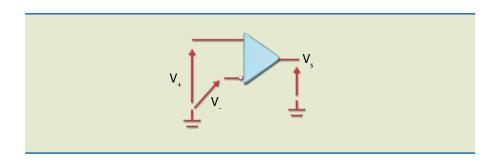

**1 e 2: Comparadores** – São elementos que promovem uma resposta na saída pela comparação das entradas: se  $V_+ > V_-$ , a saída será alta; se  $V_+ < V_-$ , será zero (figura 8.5).

**Figura 8.5** Comparador.

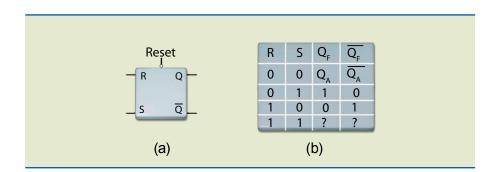

**3:** *Flip-flop* RS (FF RS) – É um biestável (figura 8.6a) que muda de estado de acordo com o nível das entradas e com a tabela verdade (TV) da figura 8.6b.

Figura 8.6

a) Flip-flop RS e

b) tabela verdade.

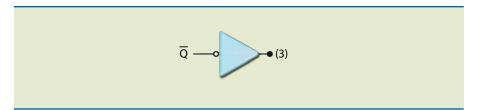

**4:** *Buffer* **de saída** – É o estágio de potência do 555, responsável pela razoável capacidade de corrente que esse dispositivo pode fornecer ou consumir (aproximadamente 200 mA).

**Figura 8.7**Buffer de saída.

5: Transistor de descarga — Opera como chave nas seguintes situações: quando  $\overline{Q}$  = 1, satura descarregando o capacitor externo; quando  $\overline{Q}$  = 0, atua como chave aberta.

Figura 8.8

Transistor de descarga:

- a) saturado e

- b) cortado.

# 8.1 Circuito integrado 555 como monoestável

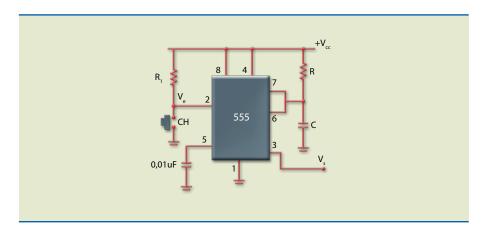

Como vimos no capítulo 7, um circuito monoestável tem dois estados: um estável e um instável; trata-se do primeiro modo de operação. A figura 8.9a mostra o circuito básico e a figura 8.9b, os componentes internos desse circuito.

**Figura 8.9a**Cl 555 como monoestável: circuito básico.

Figura 8.9b

CI 555 como monoestável:

circuito com diagrama

de blocos interno.

Observe, na figura 8.9b, as tensões de referência nas entradas dos comparadores. A tensão de valor  $^2/_3$   $V_{CC}$  está aplicada na entrada inversora (pino 5) do comparador 1 e é comparada com a tensão não inversora (pino 6), que é a tensão no capacitor. A tensão de referência de valor  $^{V}$ cc/ $^{3}$  está aplicada na entrada não inversora do comparador 2 e é comparada com a tensão no pino 2.

Para o circuito em análise, a condição estável ocorre quando  $V_S$  = 0, pois nesse caso a base do transistor TR está com nível alto e o transistor saturado; portanto, o capacitor C não consegue se carregar. Se a chave CH está aberta, a tensão no pino 2 passa a valer  $V_{CC}$ , maior que  $V_{CC}/3$ ; logo, S = 0.

Como estamos admitindo que a saída é zero, podemos concluir que o transistor interno está saturado, e, assim, a tensão nos pinos 6 e 7 vale zero, apresentando valor menor que  $^2/_3$   $V_{CC}$ ; portanto, R = 0. Como as entradas do FF são iguais a zero, o estado é mantido (ver, na figura 8.6b, a TV do FF RS), e a saída permanece em zero indefinidamente.

Se a chave CH é pressionada momentaneamente, o pino 2 passa a valer zero, o que faz com que a saída do comparador 2 e, portanto, a entrada S sejam 1. Essas condições (S = 1 e R = 0) levam FF a ter valor 1 e, logo,  $\overline{Q}$  = 0, cortando TR e impondo 1 ( $V_{CC}$ ) na saída. Observe que, mesmo quando a chave é aberta, S = R = 0, o que mantém o estado atual.

A partir daí, o capacitor começa a se carregar com constante de tempo  $R \cdot C$ , o que leva a tensão a tender para  $+V_{CC}$ . Quando a tensão no capacitor, que é a mesma do pino 6, é superior a 2/3  $V_{CC}$ , temos R = 1 e S = 0, o que impõe Q = 0 e, portanto,  $\overline{Q} = 0$ . Como consequência, TR satura, descarregando de modo instantâneo o capacitor e fazendo a saída reduzir a zero. A figura 8.10 mostra graficamente a operação do monoestável.

Pino 3 (saída)

Pino 6 (pino 7, capacitor)

Ti

Figura 8.10

Formas de onda no monoestável.

A duração do estado instável é determinada por:

$$T_i = 1.1 \cdot R \cdot C$$

### Observações

1. O fabricante recomenda que o valor do resistor de temporização (R) não seja baixo  $R \ge 1$  K, por questões de segurança), para evitar a saturação do transistor, pois quando o TR está saturado, a corrente que circula por ele é determinada por:

$$I_{Csat} = \frac{V_{CC}}{R}$$

**2.** A duração do pulso de disparo (tempo que o pino 2 fica em zero) deve ser menor que a duração da temporização  $(T_i)$ .

# 8.1.1 Aplicações do monoestável

Existem inúmeras aplicações do circuito monoestável. Vamos analisar duas delas: como temporizador e como divisor de frequências.

### Temporizador

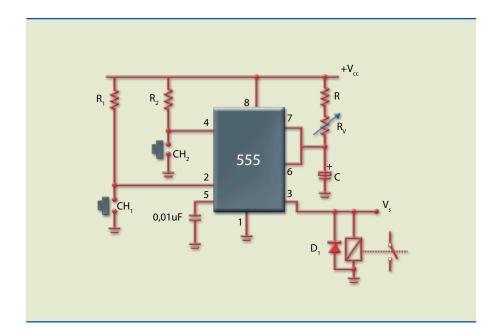

Quando usado como temporizador (*timmer*), o circuito permite ligar e desligar automaticamente uma carga (lâmpada, motor, alarme etc.) durante um intervalo que pode ser alterado por meio de ajuste do tempo.

CAPÍTULO 8

Observe a figura 8.11, que mostra o circuito básico para acionamento de um relé. A chave CH1 dispara o circuito e inicia a contagem do tempo, e a chave CH2 interrompe a contagem e zera o tempo. A resistência de temporização é a soma de R e  $R_V$ . Desse modo, é possível variar o tempo do contador. O diodo  $D_1$  não é funcional; ele protege a saída do dispositivo quando a saída está em zero.

**Figura 8.11**Temporizador.

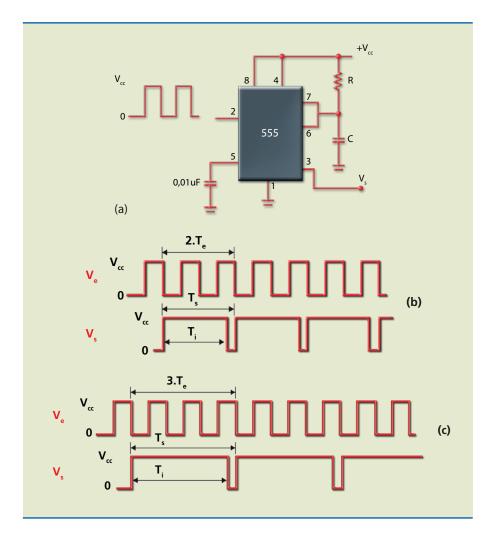

## Divisor de frequências

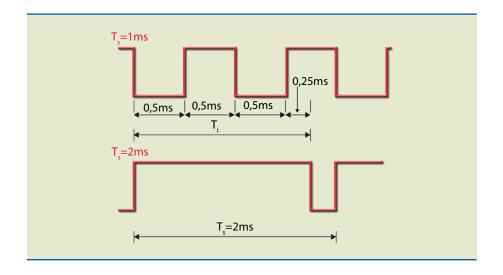

É possível ajustar o tempo de temporização  $(T_i)$  no circuito básico da figura 8.9a, de maneira que ele passe a operar como divisor de frequências. Nessas condições, o sinal de entrada tem frequência f e o sinal de saída,

$\frac{f}{n}$ , em que n é um número inteiro (2, 3, 4...).

No circuito da figura 8.12a, o sinal de entrada tem frequência  $f_e \left( T_e = \frac{1}{f_e} \right)$

Assim,  $T_i$  deve ser calculado prevendo que, no instante em que a saída estiver em zero, a entrada tem de estar em alta. As figuras 8.12b e 8.12c mostram dois casos, como divisor por 2 e como divisor por 3, respectivamente.

### Exemplo

Considere, na figura 8.12a, que o sinal de entrada tem frequência de 1 kHz ( $T_e = 1$  ms). Calcule R para que a saída tenha frequência de 500 Hz ( $T_s = 2$  ms).

Dado: C = 100 nF.

**Figura 8.12**Divisor de frequências.

Solução:

Existem diferentes valores de R que podem resultar em um divisor por 2.

A figura 8.13 apresenta o sinal de entrada e o de saída.

**Figura 8.13**Exemplo de divisor por 2 com entrada de frequência | kHz.

Nessa figura, vamos admitir que  $T_i$  = 1,75 ms (existem outros valores que satisfazem a solução). Nessas condições, R pode ser calculado.

Como  $T_i = 1,1 \cdot R \cdot C$ , então:

$$R = \frac{1,75 \cdot 10^{-3}}{1,1 \cdot 100 \cdot 10^{-9}} \cong 16 \text{ k}$$

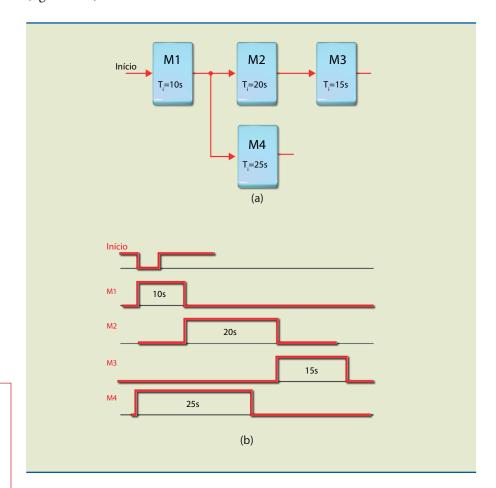

### 8.1.2 Cadeia de monoestáveis

Essa configuração é chamada de cadeia porque vários monoestáveis estão interligados em sequência, de maneira que um monoestável dispara o seguinte, enquanto está ocorrendo a descida do pulso. A finalidade principal é permitir que sejam ligadas atividades sequenciais com duração determinada de tempo (figura 8.14).

Figura 8.14

Cadeia de monoestáveis:

a) diagrama de blocos e

b) diagrama de tempos.

O disparo pela bordaacontece quando a tensão

no pino 2 (trigger) muda

de +V<sub>CC</sub> para zero, e essa

variação é transformada

em um pulso por meio de

um circuito diferenciador

(R<sub>1</sub> e C<sub>1</sub> na figura 8.15).

Tal procedimento é usado

para que a saída de um

monoestável dispare o

monoestável subsequente

(cadeia de monoestáveis).

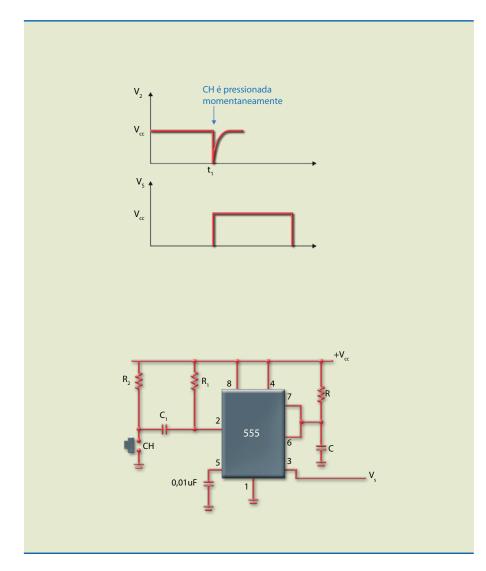

Quando desejamos que ocorra disparo pela borda do pulso, basta colocarmos um diferenciador na entrada  $R_1$  e no capacitor  $C_1$  (figura 8.15). A chave CH, ao ser pressionada, liga o capacitor ao terra, fazendo com que no pino 2 momentaneamente seja aplicado 0 V, o que dispara o monoestável, iniciando a temporização.  $C_1$ , então, começa a se carregar por  $R_1$ .

Figura 8.15

Disparo pela borda no circuito do monoestável

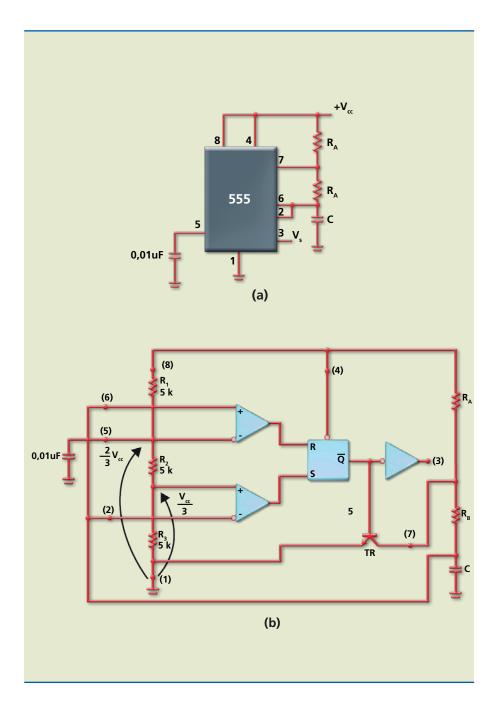

# 8.2 Circuito integrado 555 como astável

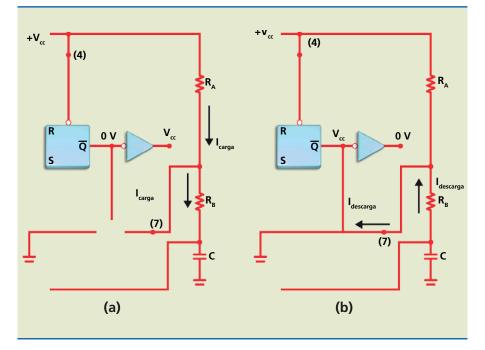

O circuito básico é apresentado na figura 8.16a, e seu diagrama de blocos internos, na figura 8.16b.

Como o circuito da figura 8.16 é um oscilador, devemos considerar uma saída em cada instante e analisar o circuito a partir desse ponto. Nessa análise, vamos levar em conta as seguintes informações: saída alta (Q=1); capacitor carregando-se ( $\overline{Q}=0$ ); transistor interno cortado com tensão tendendo a  $+V_{CC}$  (figura 8.17a).

Quando há tensão em C, existe tensão em  $V_C = V_2 = V_6$ . Nesse momento, se a tensão em C é maior que

$$\frac{2}{3}V_{CC}$$

, então R = 1 e S = 0, o que impõe: Q = 0 (*reset*) e  $\overline{Q}$  = 1.

Figura 8.16

Astável:

a) circuito básico e

b) circuito com diagrama

de blocos interno.

Com isso, a saída (pino 3) vai a zero e o transistor  $\mathsf{TR}$  satura, fazendo com que o capacitor se descarregue por meio de  $\mathsf{R}_\mathsf{B}$  e do transistor interno (figura 8.17b).

Quando <u>a</u> tensão em C fica abaixo de  $\frac{V_{CC}}{3}$ , então R = 0 e S = 1, o que impõe: Q = 1 e  $\overline{Q}$  = 0.

Desse modo, o transistor interno é **levado à condição de corte** e o capacitor volta a se carregar (a partir de Vcc/3), e o ciclo se repete.

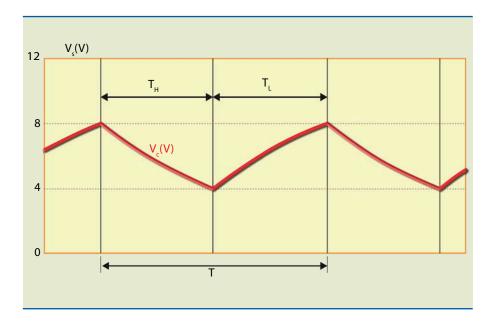

A figura 8.18 mostra as formas de onda no capacitor e na saída do circuito da figura 8.16a.

Figura 8.17

Capacitor:

- a) carga e

- b) descarga.

Figura 8.18

Formas de onda da tensão na saída (V<sub>s</sub>) e no capacitor (V<sub>C</sub>) do circuito da figura 8.16a.

O período das oscilações é dado por:

$$T = T_H + T_L$$

em que  $T_H$  é o tempo alto e  $T_L$  o tempo baixo. Assim:

$$T_{H} = 0.69 \cdot (R_{A} + R_{B}) \cdot C \cdot e \cdot T_{L} = 0.69 \cdot R_{A} \cdot C.$$

Um transistor élevado à condição de corte (ou é cortado) quando torna todas as correntes nulas e tenta aplicar novamente tensão no circuito.

Se  $R_B >> R_A$ , os tempos alto e baixo serão aproximadamente iguais, sempre. Lembre que a resistência  $R_A$  deve ser maior que 1 k $\Omega$  para proteger o transistor interno.

Genericamente, o tempo pode ser determinado pelas expressões:

$$T_H = 0.69 \cdot R_{carga} \cdot C \cdot e \cdot T_L = 0.69 \cdot R_{descarga} \cdot C.$$

$R_{carga}$  é a resistência que o capacitor enxerga durante a carga e  $R_{descarga}$  a resistência que o capacitor enxerga na descarga.

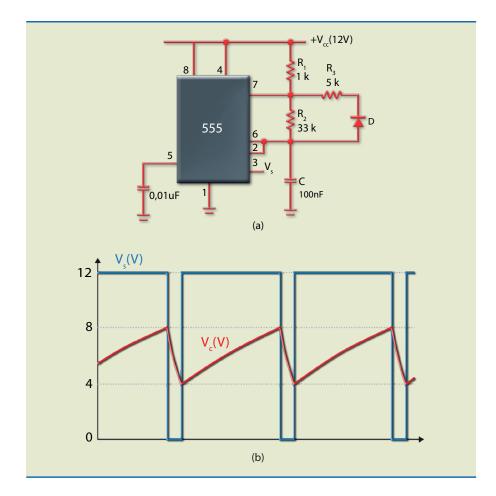

Observe que, se os caminhos da carga e da descarga puderem ser controlados, é possível administrar os tempos alto e baixo. Por exemplo, no circuito da figura 8.19a, a carga do capacitor é feita por  $R_1$  +  $R_2$  (34 k $\Omega$ ) e a descarga, por  $R_2$ // $R_3$  (33 k $\Omega$ //5 k $\Omega$ ), resultando nas formas de onda da figura 8.19b.

Figura 8.19

a) Circuito com tempo alto

muito maior que o baixo e

b) formas de onda.

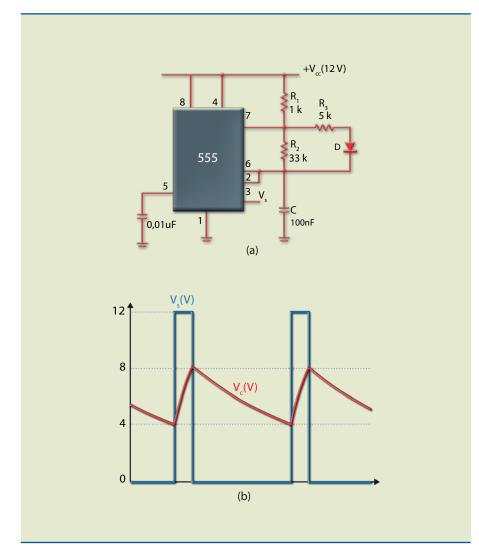

No entanto, se o diodo for invertido, o tempo alto será muito menor que o baixo, como mostra a figura 8.20a. O diodo D conduz na carga do capacitor, que é feita por R<sub>1</sub> + (R<sub>2</sub>//R<sub>3</sub>), ou seja, 1 k $\Omega$  + (33 k $\Omega$ //5 k $\Omega$ ). Na descarga, o diodo corta e o capacitor descarrega por R<sub>2</sub> (33 k $\Omega$ ), resultando nas formas de onda da figura 8.20b.

### Figura 8.20

a) Circuito com tempo alto muito menor que o baixo eb) formas de onda.

# 8.3 Circuito integrado 555 como biestável

O circuito integrado 555 pode ser usado como biestável controlado por tensão. Nessa configuração, ele é chamado de Schmitt Trigger. Observe, na figura 8.21, que o sinal de entrada é aplicado nos pinos 2 e 6, por meio de um capacitor  $C_1$ . Os resistores  $R_1$  e  $R_2$  polarizam as entradas 2 e 6 com a tensão:

$$V_2 = V_6 = \frac{R_2}{R_1 + R_2} \cdot V_{cc}$$

Quando  $R_1 = R_2 = R$ , a tensão de polarização é  $V_{cc}/2$ . Vimos que, se a tensão no pino 6 for maior que 2/3  $V_{cc}$ , R = 1; se maior que 1/3  $V_{cc}$ , S = 0 e, portanto,  $V_S = 0$ .

Quando a tensão nos pinos 6 e 2 fica menor que  $^{1}/_{3}$   $V_{cc}$ , temos R = 0 e S = 1, o que impõe na saída a tensão  $V_{CC}$ .